DDR4学习笔记

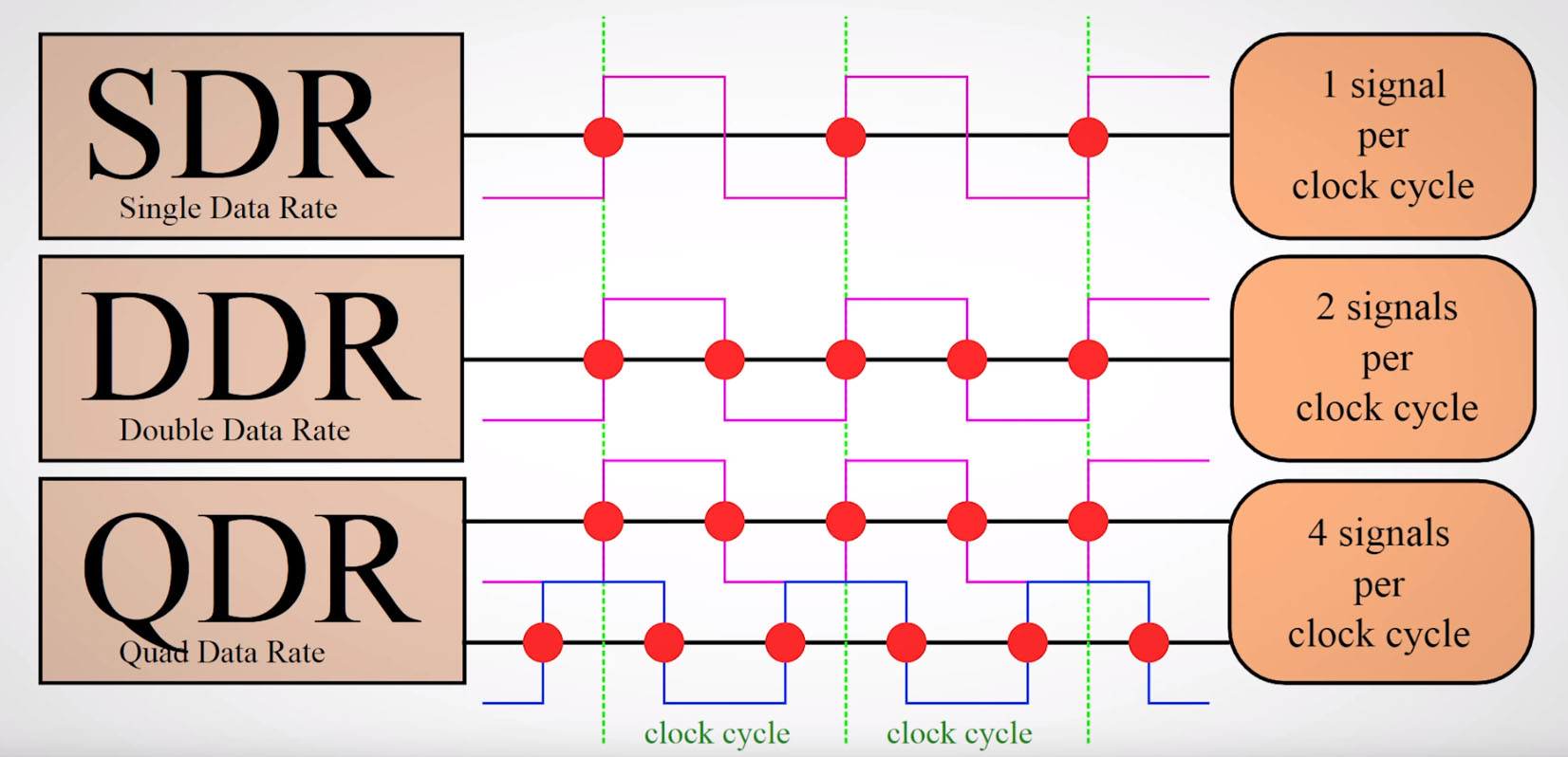

First, the basics. While memory frequency is measured in Hertz, or cycles per second, the unit for memory timings is just plain cycles. To convert clock cycles to a measurement of time requires knowing the frequency of the memory. This is listed in MHz, or units of 1,000,000Hz. 3200MHz memory has a clock frequency of 3,200,000,000 cycles per second, so the time for a cycle to complete should be (1/3,200,000,000) seconds. However, modern memory is DDR (double data rate), meaning data is transferred on the rising and falling edge of each clock, so advertised frequencies are twice the real clock frequency. That’s why when you set memory to 3200MHz in BIOS, CPU-Z will show 1600MHz. Therefore the time is really (1/(3,200,000,000/2)) seconds. If our example memory has a CL timing of 16 clock cycles, this translates to (16 * (1/(3,200,000,000/2))) seconds, or .00000001 seconds, or 10 nanoseconds.

First, the basics. While memory frequency is measured in Hertz, or cycles per second, the unit for memory timings is just plain cycles. To convert clock cycles to a measurement of time requires knowing the frequency of the memory. This is listed in MHz, or units of 1,000,000Hz. 3200MHz memory has a clock frequency of 3,200,000,000 cycles per second, so the time for a cycle to complete should be (1/3,200,000,000) seconds. However, modern memory is DDR (double data rate), meaning data is transferred on the rising and falling edge of each clock, so advertised frequencies are twice the real clock frequency. That’s why when you set memory to 3200MHz in BIOS, CPU-Z will show 1600MHz. Therefore the time is really (1/(3,200,000,000/2)) seconds. If our example memory has a CL timing of 16 clock cycles, this translates to (16 * (1/(3,200,000,000/2))) seconds, or .00000001 seconds, or 10 nanoseconds.

The equation is (1/(advertised frequency/2)) * timing in cycles = timing in seconds. For a DDR3-1600 kit, a CL of 9 translates to 11.25ns, actually slower than our previous example. Latencies have gradually increased over the years with the physical distance that signals have to travel (the speed of light is a hard limit), but frequency has increased as well, and therefore performance has still improved. Frequency is very important, but it’s just one element of performance, as with CPUs.

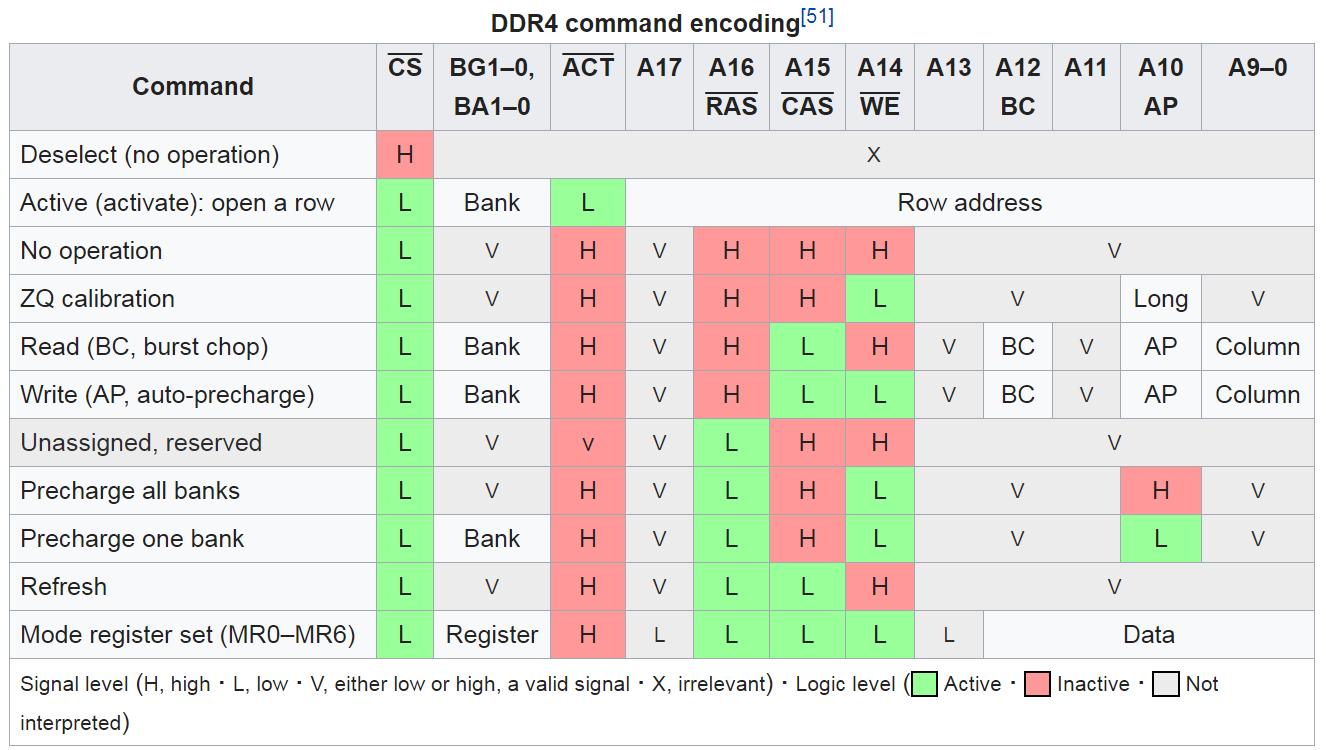

There are many, many different timings, but they deal with a fairly small list of commands: when they can be issued, how long it takes for them to execute, how many cycles pass before a response. Here’s a table of DDR4 commands copied from Wikipedia:

The important signals from the top row are ACT (Activate), RAS (Row Access Strobe), CAS (Column Access Strobe), and WE (Write Enable). RAS and CAS are often referred to simply as column and row address because they aren’t actually strobes; the terminology is a holdover. These are Active-Low signals, so they can be either H(igh) or L(ow), 1 or 0. Together they form a four-bit code that specifies a command to be executed. The signals have changed a bit over the years, but for the most part DDR4 has the same list of commands that SDRAM has always had, and therefore many of the same timings. For some background information on stuff like banks, rows, and columns, this venerable 2010 article from Anandtech is a good overview of what SDRAM actually is and how it functions.